How To Prevent Glitches In Circuits - One method adjusts threshold voltages through ion implantation and oxide. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. This paper presents different techniques for reducing glitch power in digital circuits. Engineers are creating new ways to fight glitches. The aim of this study is to minimize glitch power as glitch. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. The capacitor retains the previous sampled. Glitches can be caused by.

This paper presents different techniques for reducing glitch power in digital circuits. Glitches can be caused by. The capacitor retains the previous sampled. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. The aim of this study is to minimize glitch power as glitch. One method adjusts threshold voltages through ion implantation and oxide. Engineers are creating new ways to fight glitches. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output.

Engineers are creating new ways to fight glitches. The capacitor retains the previous sampled. Glitches can be caused by. This paper presents different techniques for reducing glitch power in digital circuits. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. The aim of this study is to minimize glitch power as glitch. One method adjusts threshold voltages through ion implantation and oxide.

Distortion and glitches in digital circuits Stock Photo Alamy

Engineers are creating new ways to fight glitches. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. The capacitor retains the previous sampled. Glitches can be caused by. This paper presents different techniques for reducing glitch power in digital circuits.

Smart Ways To Prevent Short Circuits Zameen Blog

In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. The capacitor retains the previous sampled. This paper presents different techniques for reducing glitch power in digital circuits. Engineers are creating new ways to fight glitches. Glitches can be caused by.

Premium Photo Distortion and glitches in digital circuits

The aim of this study is to minimize glitch power as glitch. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. Engineers are creating new ways to fight glitches. Glitches can be caused by. This paper presents different techniques for reducing glitch power in digital circuits.

Premium Photo Distortion and glitches in digital circuits

This paper presents different techniques for reducing glitch power in digital circuits. Glitches can be caused by. The aim of this study is to minimize glitch power as glitch. The capacitor retains the previous sampled. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard.

Premium Photo Distortion and glitches in digital circuits

Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. Engineers are creating new ways to fight glitches. One method adjusts threshold voltages through ion implantation and oxide. This paper presents different techniques for reducing glitch power in digital circuits. In this paper, we try to reduce the glitch power in the circuits.

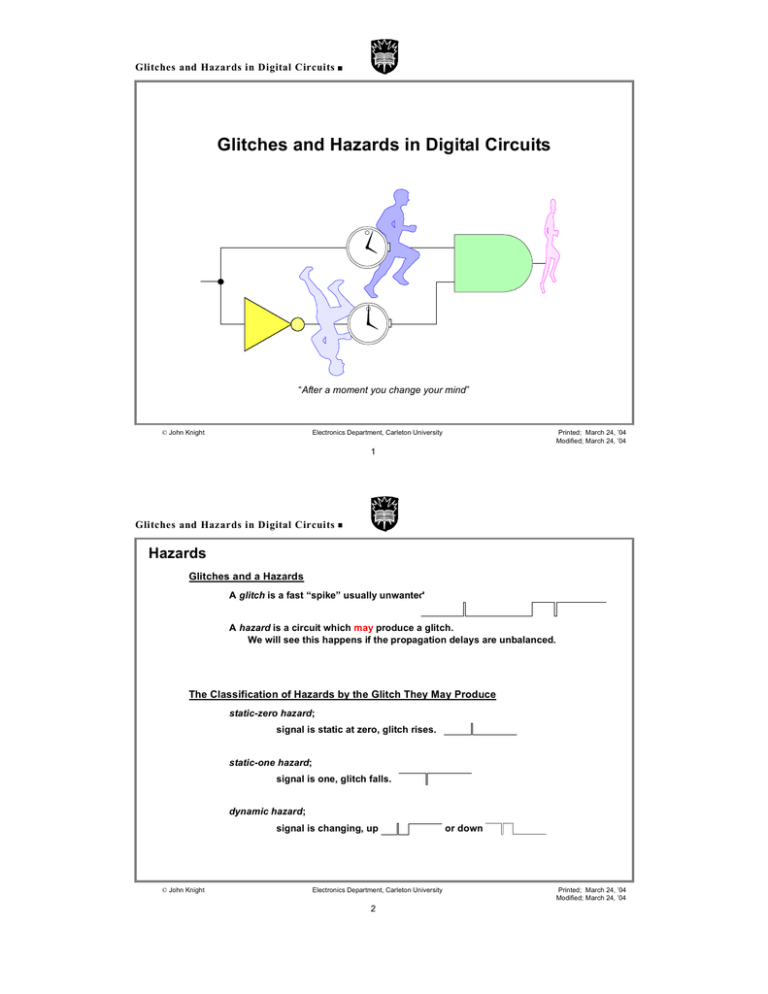

Glitches and Hazards in Digital Circuits Hazards Glitches and a Hazards

Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. Glitches can be caused by. Engineers are creating new ways to fight glitches. The capacitor retains the previous sampled. One method adjusts threshold voltages through ion implantation and oxide.

5 Effective Ways To Prevent Short Circuits Bproperty

This paper presents different techniques for reducing glitch power in digital circuits. The aim of this study is to minimize glitch power as glitch. The capacitor retains the previous sampled. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. Engineers are creating new ways to.

Distortion and glitches in digital circuits Stock Photo Alamy

This paper presents different techniques for reducing glitch power in digital circuits. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. The capacitor retains the previous sampled. Glitches can be caused by. The aim of this study is to minimize glitch power as glitch.

Premium Photo Distortion and glitches in digital circuits

This paper presents different techniques for reducing glitch power in digital circuits. Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. Engineers are creating new ways to fight glitches. One method adjusts threshold voltages through ion implantation and oxide. The capacitor retains the previous sampled.

5 Effective Ways To Prevent Short Circuits Bproperty

One method adjusts threshold voltages through ion implantation and oxide. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. The aim of this study is to minimize glitch power as glitch. Circuit is in hold mode, preventing any dac major carry glitches from propagating to.

One Method Adjusts Threshold Voltages Through Ion Implantation And Oxide.

The capacitor retains the previous sampled. In this paper, we try to reduce the glitch power in the circuits and analyze the various available techniques such as gate freezing, hazard. This paper presents different techniques for reducing glitch power in digital circuits. The aim of this study is to minimize glitch power as glitch.

Glitches Can Be Caused By.

Circuit is in hold mode, preventing any dac major carry glitches from propagating to the s&h output. Engineers are creating new ways to fight glitches.